# ECE 448 Midterm Exam – Solutions for Group 1 Monday, March 2, 2020

## **Problem 1**

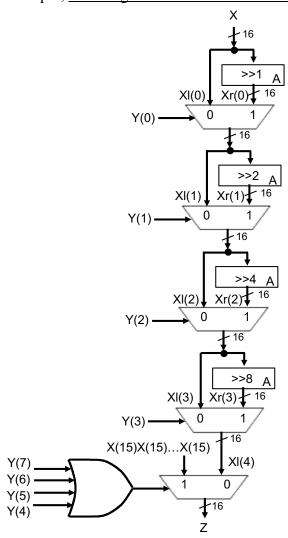

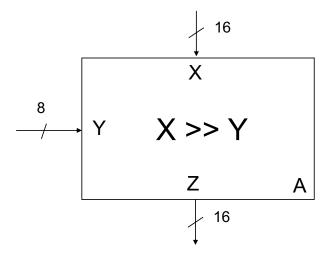

Perform the following tasks for

## a combinational Variable Arithmetic Shifter Right,

with the block diagram shown in Fig. 1.

- A. Fill in the blanks in the code of this component given on the next page.

- B. Draw a symbol of this component with the correct

- number

- direction, and

- widths

of ALL inputs and outputs.

Name each input and output, matching the VHDL code on the next page.

Fig. 1: Block diagram of a combinational Variable Arithmetic Shifter Right

#### Answer A:

```

library IEEE;

use IEEE.STD LOGIC 1164.all;

ENTITY fixed shifter right IS

GENERIC(L : INTEGER := 1);

PORT (

a : IN STD LOGIC VECTOR(15 downto 0);

y : OUT STD LOGIC VECTOR(15 downto 0)

);

END fixed shifter right;

ARCHITECTURE dataflow OF fixed shifter right IS

BEGIN

y(15-L downto 0) \ll a(15 downto L);

y(15 \text{ downto } 15-L+1) \le \text{OTHERS} \implies a(15);

END dataflow;

library IEEE;

use IEEE.STD LOGIC 1164.all;

ENTITY variable shifter right IS

PORT (

X : IN STD LOGIC VECTOR(15 downto 0);

Y : IN STD_LOGIC_VECTOR(7 downto 0);

Z : OUT STD LOGIC VECTOR (15 downto 0)

);

END variable shifter right;

ARCHITECTURE mixed OF variable shifter right IS

TYPE array16 IS ARRAY (0 to 4) OF STD LOGIC VECTOR (15 DOWNTO 0);

SIGNAL X1 : array16;

SIGNAL Xr : array16;

BEGIN

X1(0) <= X;

G: FOR i IN 0 TO 3 GENERATE

SHIFT I: ENTITY work.fixed shifter right(dataflow)

GENERIC MAP (L \Rightarrow 2**i)

PORT MAP ( a \Rightarrow xl(i),

y \Rightarrow Xr(i);

Xl(i+1) \le Xr(i) WHEN Y(i)='1' ELSE Xl(i);

END GENERATE;

```

$$Z \leftarrow OTHERS \Rightarrow X(15)$$

WHEN (Y(7) OR Y(6) OR Y(5) OR Y(4)) = '1' ELSE X1(4);

END mixed;

## **Answer B:**

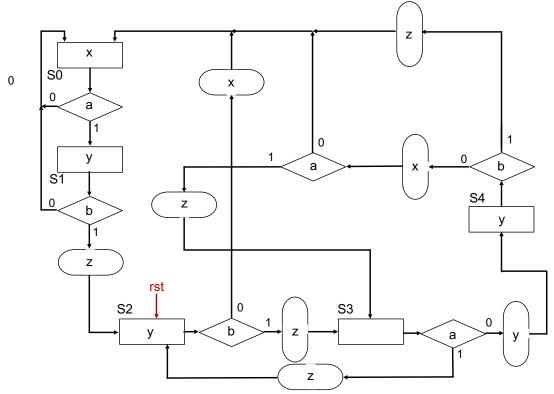

## Problem 2

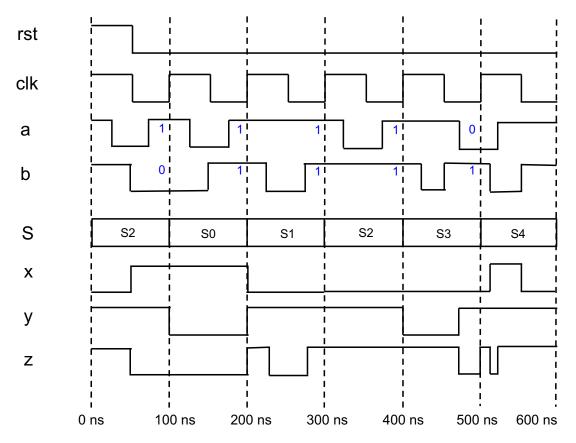

Assuming the controller described using the given below ASM chart:

- A. Supplement timing waveforms given on the next page with the values of the **state S**, and the values of the **outputs x**, **y**, and **z**.

- B. Fill in the blanks in the <u>fragment</u> of the code of this component given on the next page.

## Answer A:

## Be careful regarding the initial value of the state S after reset!

#### **Answer B:**

```

ARCHITECTURE behavioral of Controller IS

TYPE state IS (S0, S1, S2, S3, S4);

SIGNAL state reg, state next: state;

BEGIN

P1: PROCESS(clk, rst)

BEGIN

IF(rst = '1') THEN

state reg <= S2;</pre>

ELSIF rising edge(clk) THEN

state req <= state next;</pre>

END IF;

END PROCESS;

Next State Output:

PROCESS (state reg, a, b)

BEGIN

state next <= state reg;</pre>

x <= '0';

y \le '0';

z <= '0';

CASE state reg IS

WHEN S4 =>

y <= '1';

if b='1' then

z <= '1';

state next <= S0;</pre>

else

x <= '1';

if a = '1' then

z <= '1';

state next <= S3;</pre>

else

state next <= S0;</pre>

end if;

end if:

```

Please provide the code only for the case when state reg = S4.

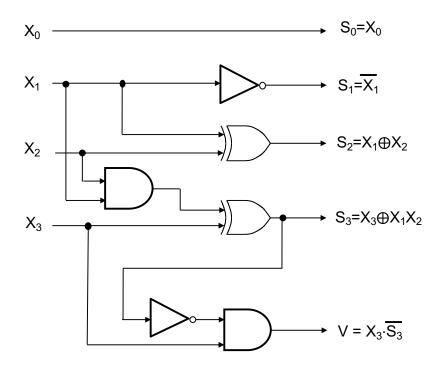

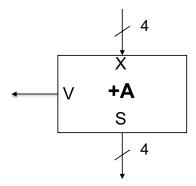

## Problem 3

Perform the following tasks for a component

taking a 4-bit input X of the type std\_logic\_vector, adding to it a constant, given by the generic A of the type integer (in the range -8 to 7), and returning the sum S of the type std\_logic\_vector and the overflow V of the type std\_logic.

- A. Draw a symbol of this component with the correct

- number

- direction, and

- widths

of ALL inputs and outputs.

Name each input and output.

- B. Write the full synthesizable code of this design entity, including entity declaration and architecture body, using the package numeric\_std.

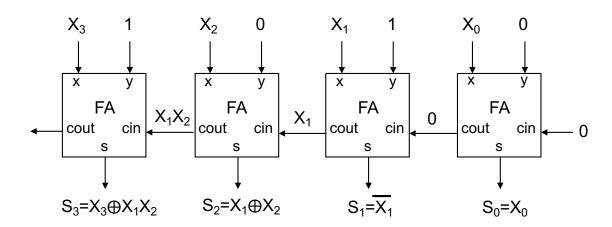

- C. **(bonus)** Draw an internal block diagram of this component, composed of medium logic components and/or basic logic gates for the case of A=-6.

## **Answer A:**

Answer B:

You can use the following table of overloaded operators in the IEEE numeric\_std package

| overloaded<br>operator                                | description                | data type<br>of operand a                                  | data type<br>of operand b                                  | data type<br>of result                   |

|-------------------------------------------------------|----------------------------|------------------------------------------------------------|------------------------------------------------------------|------------------------------------------|

| abs a<br>- a                                          | absolute value<br>negation | signed                                                     |                                                            | signed                                   |

| a * b a / b a mod b a rem b a + b a - b               | arithmetic<br>operation    | unsigned<br>unsigned, natural<br>signed<br>signed, integer | unsigned, natural<br>unsigned<br>signed, integer<br>signed | unsigned<br>unsigned<br>signed<br>signed |

| a = b<br>a /= b<br>a < b<br>a <= b<br>a > b<br>a >= b | relational<br>operation    | unsigned<br>unsigned, natural<br>signed<br>signed, integer | unsigned, natural<br>unsigned<br>signed, integer<br>signed | boolean<br>boolean<br>boolean<br>boolean |

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

USE ieee.numeric_std.all;

ENTITY plusA IS

GENERIC ( A : INTEGER RANGE -8 TO 7 := -6 ) ;

PORT ( X : IN STD LOGIC VECTOR(3 downto 0);

S: OUT STD LOGIC VECTOR(3 downto 0);

V : OUT STD LOGIC);

END plusA;

ARCHITECTURE dataflow OF plusA IS

SIGNAL Sum : SIGNED(3 downto 0);

BEGIN

Sum \le signed(X) + A;

S <= std logic vector(Sum);

V \le (X(3) \text{ and to signed}(A, 4)(3) \text{ and not } Sum(3)) \text{ or}

(not X(3) and not to signed(A, 4)(3) and Sum(3));

END dataflow;

```

## **Answer C:**

## **Derivation:**

V = 1 when X negative and S positive

$$V = X_3 \cdot \overline{S_3} = X_3 \cdot (\overline{X_3 \oplus X_1 X_2})$$

## **Final Optimized Circuit:**