# An Implementation Comparison of an IDEA Encryption Cryptosystem on Two General-Purpose Reconfigurable Computers

#### Allen Michalski<sup>1</sup>, Kris Gaj<sup>1</sup>, Tarek El-Ghazawi<sup>2</sup>

<sup>1</sup> ECE Department, George Mason University <sup>2</sup> ECE Department, The George Washington University

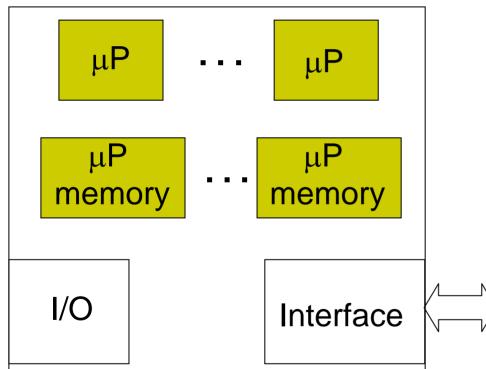

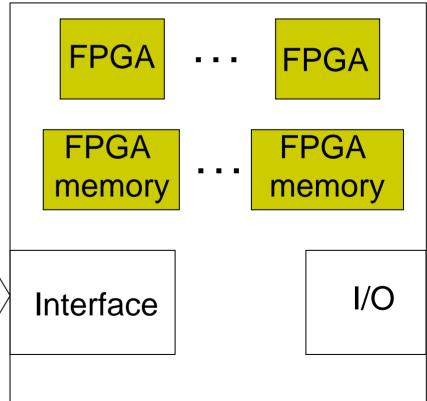

# What is a Reconfigurable Computer?

#### Microprocessor system

#### Reconfigurable processor system

#### **Characteristic Features**

- ✓ composed of traditional microprocessors and FPGAs

- ✓ programming does not require knowledge of hardware design

- ✓ permit run-time reconfiguration of FPGAs

**Examples:**

SRC-6E

Starbridge HC-36

#### **SRC and Star Bridge Systems**

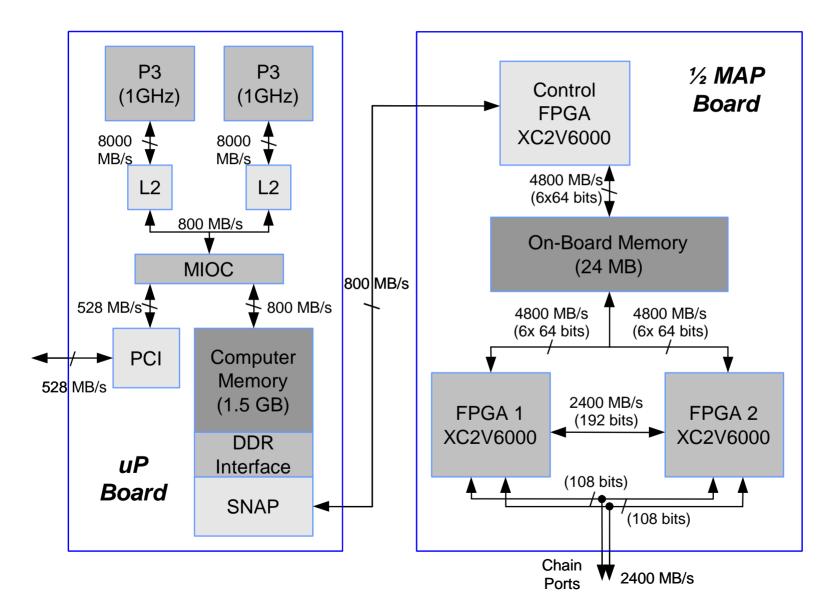

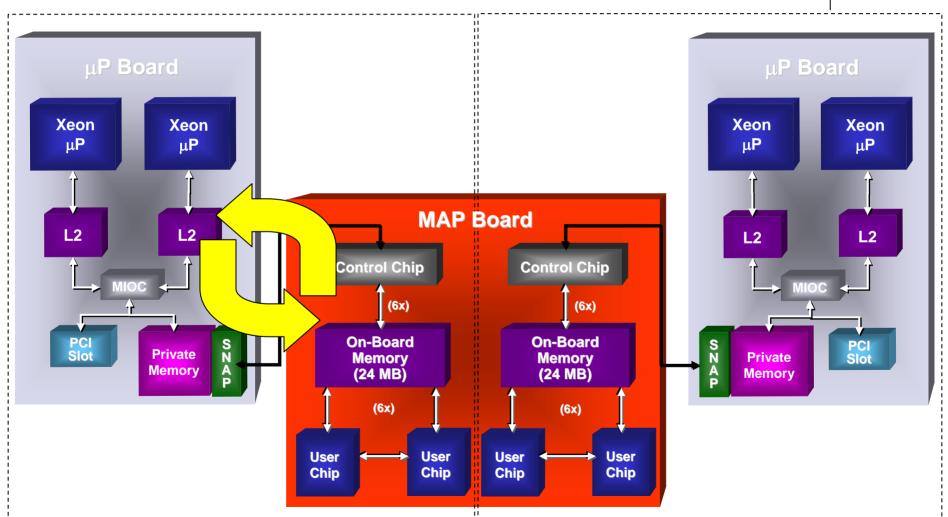

#### **SRC Hardware Architecture**

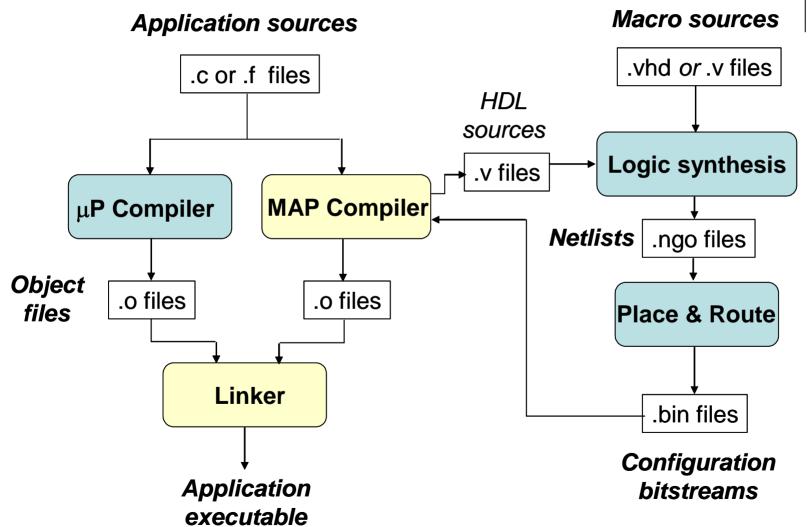

#### **SRC Compilation Process**

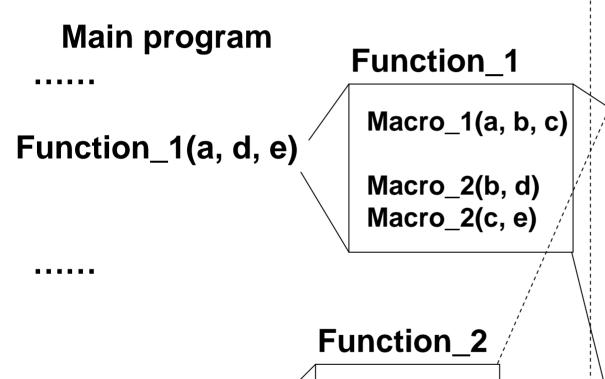

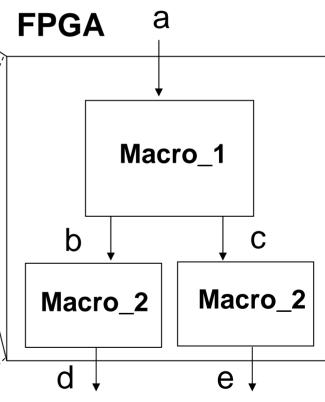

#### **SRC Programming Model**

Program in C or Fortran

Function\_2(d, e, f)

Macro\_3(s, t)

Macro\_1(n, b)

Macro\_4(t, k)

FPGA contents after the Function\_1 call

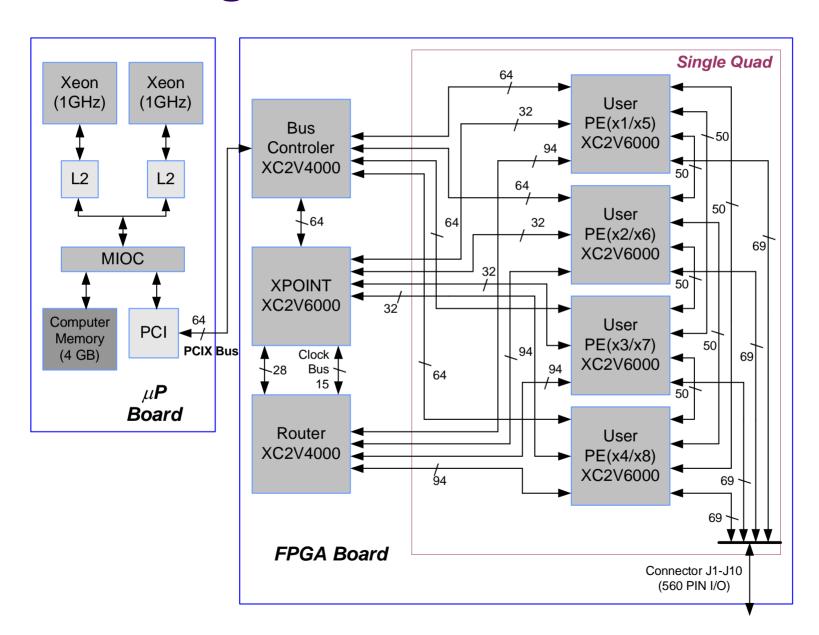

#### **Star Bridge Hardware Architecture**

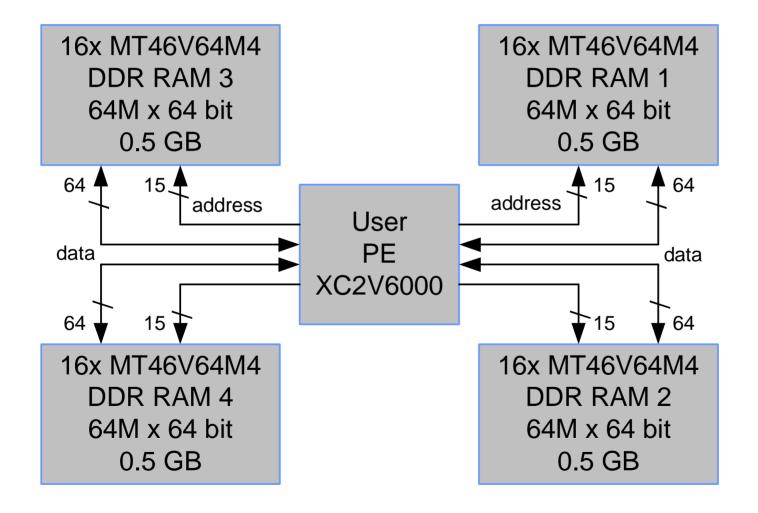

# Star Bridge Processing Element (PE)

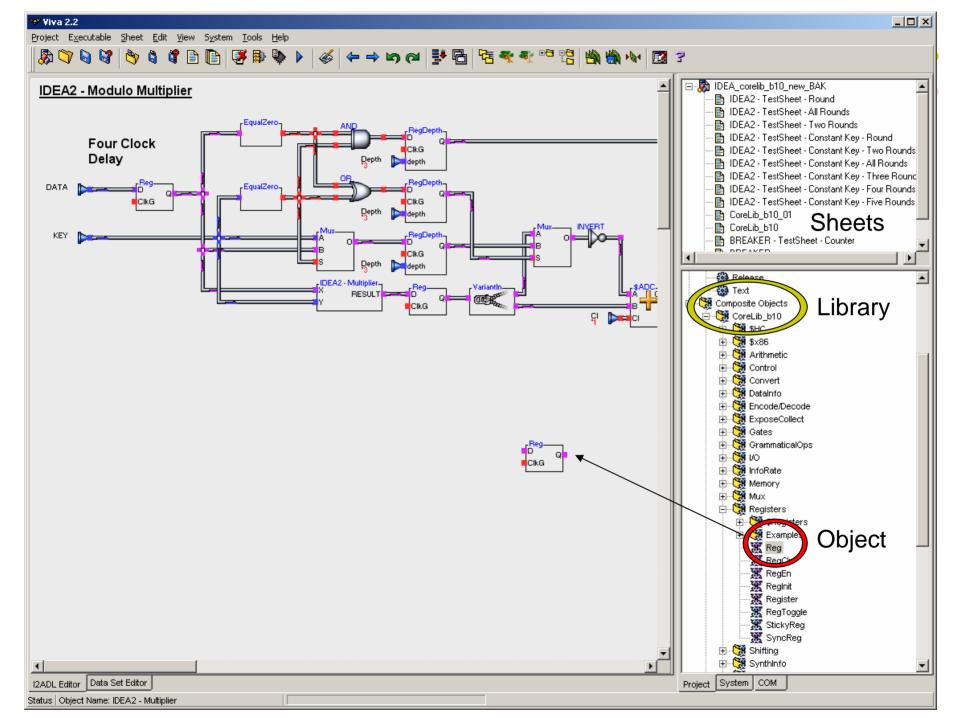

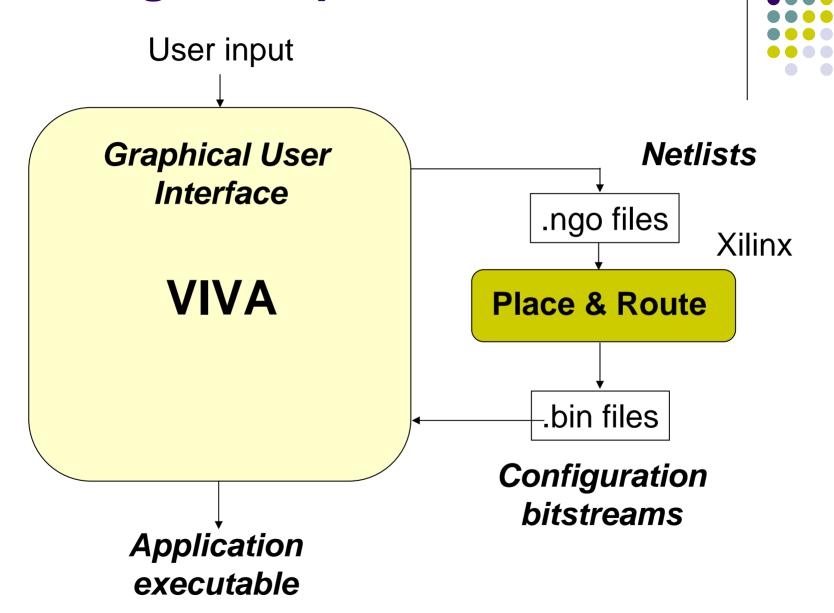

#### **Star Bridge Compilation Process**

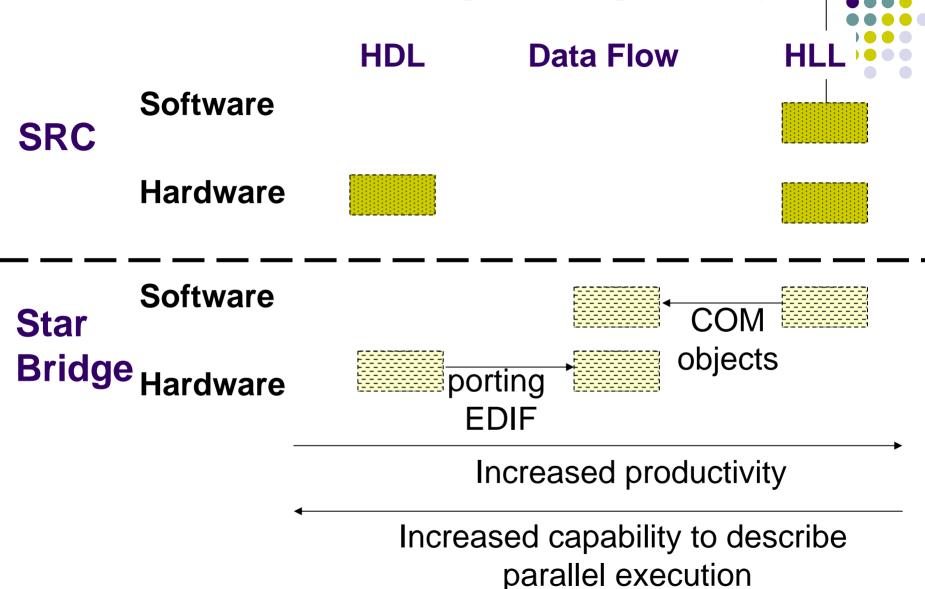

#### SRC vs. Star Bridge Design Entry

# High-Throughput Secret-Key Encryption with IDEA

#### **IDEA**

- International Data Encryption Algorithm, published in 1990

- Conventional encryption algorithm suggested to replace DES

- Largest use in PGP

- Block cipher

- 128 bit key

- 64 bit data block

- 8 ½ rounds

#### **IDEA – Three Basic Operations**

$$Y = X + K \mod 2^{16}$$

$$Y = X \cdot K \mod (2^{16}+1)$$

where 0 represents 2<sup>16</sup>

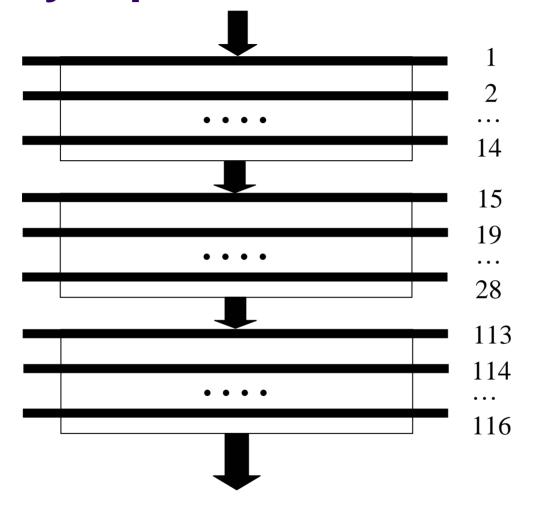

#### **Fully Pipelined Architecture of IDEA**

8.5 rounds

14 pipeline stages/round

- 116 pipeline stages

- New input & new output every clock cycle

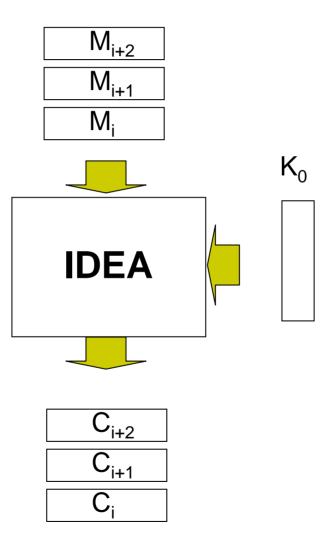

#### **High-Throughput Encryption**

. . . .

# High-Throughput Secret-Key Encryption in SRC

#### **Data Flow During Encryption**

#### **IDEA Encryption**

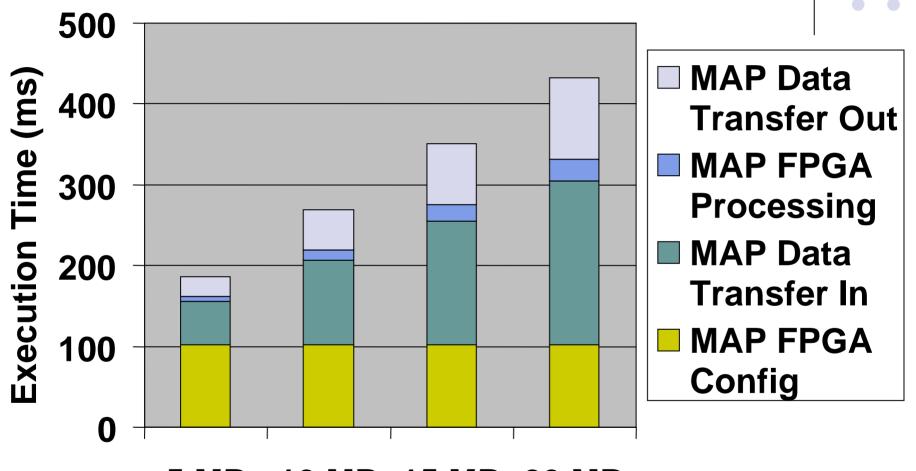

MB 10 MB 15 MB 20 MB

Amount Data Processed

#### **Problems**

- Execution time dominated by

- Configuration of the MAP FPGA and

- Data transfer between the System Common Memory and On-Board-Memory

- Preloading the configuration before execution

- Flip-flopping FPGAs during reconfiguration

### Comparison of SRC MAP vs. Pentium 4

| Data Processed  | 5MB   | 10MB  | 15MB  | 20MB  |

|-----------------|-------|-------|-------|-------|

| SRC (sec)       | 0.08  | 0.17  | 0.25  | 0.33  |

| Pentium 4 (sec) | 7.99  | 15.96 | 23.94 | 31.93 |

| SRC Speed-up    | 95.60 | 95.16 | 96.27 | 96.53 |

Pentium 4 implementation based on the Crypto++ 5.0 library

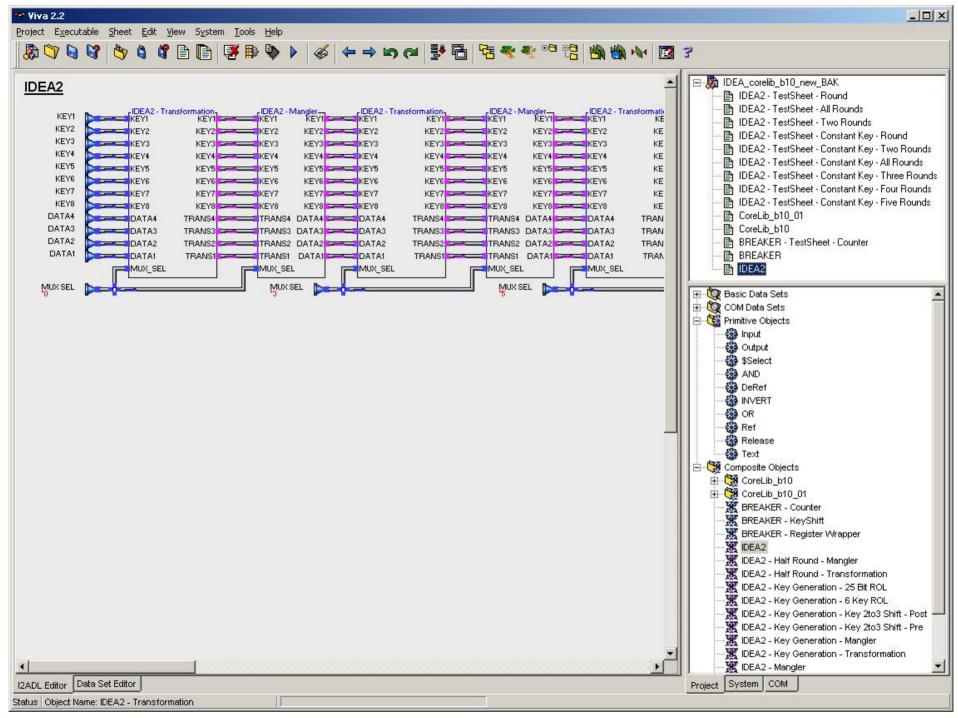

#### **IDEA** in VIVA

#### **Star Bridge Results**

- Hardware interface and software support for efficient data transfer still under development

- Unable to measure end-to-end time without file i/o, data transfer in time, or data transfer out time

- MAP FPGA Processing Time the same as on the SRC machine

#### **Results Comparison**

#### **IDEA – Compilation Time**

#### SRC

Synthesis2 min

Mapping4 min

Placing and Routing

1 hr 34 min

Star Bridge

Viva compilation time ~36 hrs

Mapping14 min

Placing and Routing

1 hr 25 min

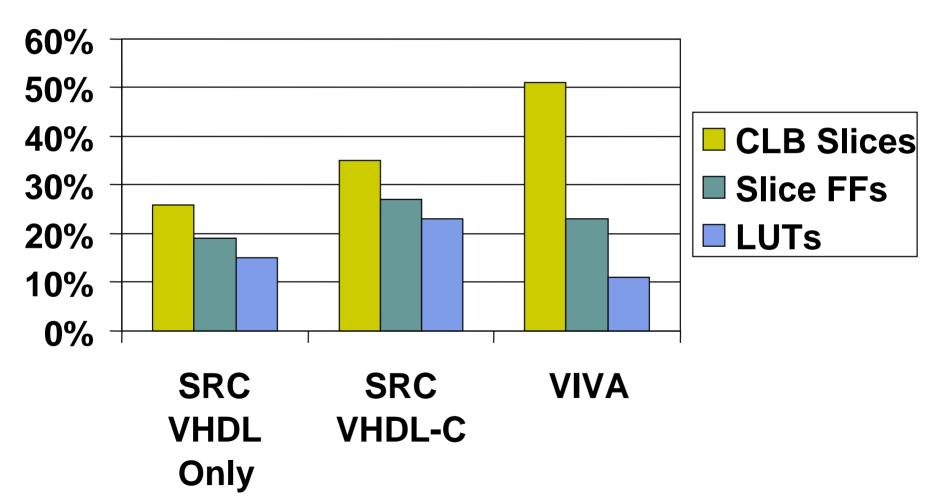

### IDEA Use of FPGA Resources Xilinx XC2V6000

#### **IDEA – Timing**

- FPGA Processing Time the same in both systems

- The same number of clock cycles

- The same maximum clock frequency 100 MHz

- The End-to-End time much smaller in SRC, but the exact comparison impossible because of the early development stage of the Star Bridge hardware and software

#### **Conclusions**

- Both platforms are unique expansions of existing paradigms

- FPGA data transfer is a significant bottleneck for I/O intensive applications, such as encryption

- SRC hardware and software more advanced

Star Bridge system still in early development state

- Two order-of-magnitude speedup versus softwareonly solution for the high-speed IDEA encryption on SRC